The FPC/Interface/luminance/Touch panel/Cover glass of our most products is customizable.

If you have any requirements, please contact us.

This 7.6-inch monochrome TFT LCD features a high resolution of 4098×2560 for crisp detail and clarity. Powered by the HX8252A00 driver IC, it delivers reliable performance, making it ideal for industrial, medical, and specialized display applications.

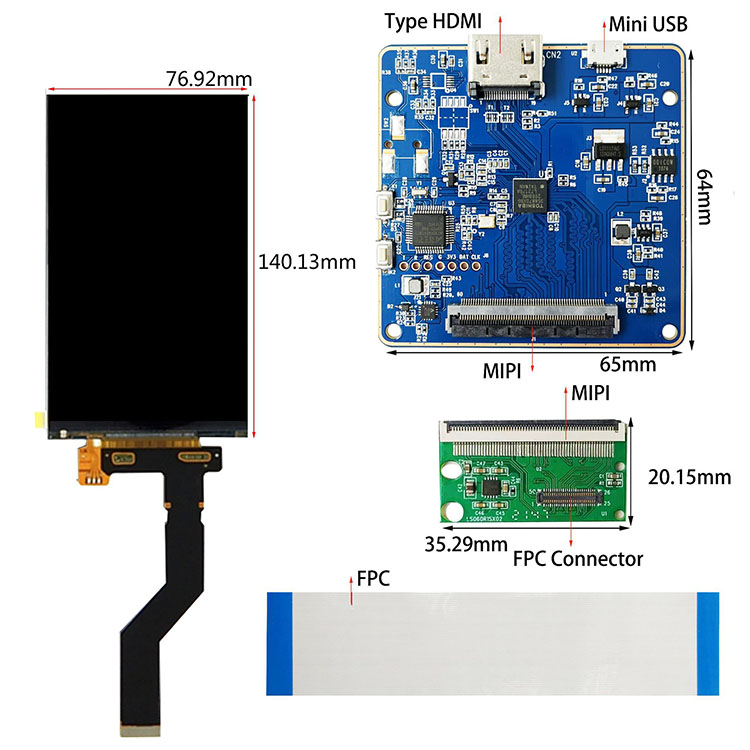

DRAWING

SPECIFICATIONS

| General Specification | |

|---|---|

| Part No. | DXQ7D6001 |

| Supplier Type | Manufacturer |

| Place of Origin | Guangdong, China |

| Brand Name | Chance |

| Outline Dimension | 174.96 (W)*113.48(H)*1.24(T) |

| Active Area | 163.92 (W)*102.4(H) |

| Pixel pitch | 0.040*0.040 |

| Resolution | 4098*2560 |

| Interface | MIPI |

| Driver IC | HX8252A00*2 |

| Color | Monochrome |

| Viewing Direction | All |

| Operating Temperature | -20°C~70°C |

| Storage Temperature | -30°C~80°C |

| Module lifetime(Hours) | 50000 |

| Interface NO. | Symbol •r | Description |

|---|---|---|

| 1 | GND | Ground |

| 2 | D2P M | MASTER MIPI data Lane 2 positive-end input |

| 3 | D2N M | MASTER MIPI data Lane 2 negative-end input |

| 4 | GND | Ground |

| 5 | DIP M | MASTER MIPI data Lane 1 positive-end input |

| 6 | DIN M | MASTER MIPI data Lane 1 positive-end input |

| 7 | GND | Ground |

| 8 | CLKP M | MASTER MIPI Clock Lane posilive-end inpui/ouipul |

| 9 | CLKN M | MASTER MIPI Clock Lane negative-end inpui/outpul |

| 10 | GND | Ground |

| 11 | DOP M | MASTER MIPI data Lane 2 positive-end inpul |

| 12 | DON M | MASTER MIPI data Lane 2 positive-end input |

| 13 | GND | Ground |

| 14 | D3P M | MASTER MIPI data Lane 3 posilive-end input |

| 15 | D3N M | MASTER MIPI data Lane 3 positive-end input |

| 16 | GND | Ground |

| 17 | D2P S | Slave MIPI data Lane 2 posilive-end input |

| 18 | D2N S | Slave MIPI data Lane 2 negative-end inpul |

| 19 | GND | Ground |

| 20 | DIP S | Slave MIPI data Lane 2 positive-end input |

| 21 | DIN S | Slave MIPI data Lane 2 negaiive-end input |

| 22 | GND | Ground |

| 23 | CLKP S | Slave MIPI Clock Lane positive-end input/oulput |

| 24 | CLKN S | Slave MIPI Clock Lane negatives?nd input/ouipul |

| 25 | GND | Ground |

| 26 | DOP S | Slave MIPI data Lane 2 posilive-end input |

| 27 | DON S | Slave MIPI data Lane 2 negative-end input |

| 28 | GND | Ground |

| 29 | D3P S | Slave MIPI data Lane 2 positive-end input |

| 30 | D3M S | Slave MIPI data Lane 2 negative-end input |

| 31 | GND | Ground |

| 32 | GND | Ground |

| 33 | TE | Tearing efleet signal to frame memory writing |

| 34 | RESET | Reset signal input lerminal(lv8) |

| 35 | NC | No connection |

| 36 | GND | Ground |

| 37 | VCC | Power supply(3v3) |

| 38 | GND | Ground |

| 39 | IOVCC | IO Power supply(lv8) |

| 40-41 | GND | Ground |

| 42 | NC | No connection |

| 43 | VSN | Negative input analog power(-5.5V) |

| 44 | NC | No connection |

| 45 | VSP | Positive input analog power(+5.5V) |

| 4649 | NC | |

| 50 | GND | Ground |